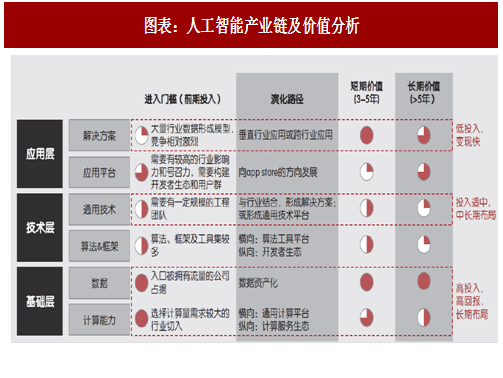

在这条产业链中,以硬件和数据为代表的基础层是构建生态的基础,价值最高,需要长期大量投入进行战略布局;通用技术层是构建技术壁垒的基础,投入适中,需要在中长期进行布局;而应用层直戳行业痛点,相对来说具有低投入变现快的特点。

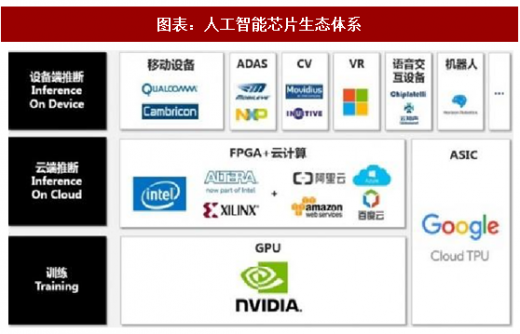

推断(inference)则分为两大类——云侧推断与端侧推断,云侧推断推断不仅要求硬件有着高性能计算,更重要的是对于多指令数据的处理能力。就比如Bing搜索引擎同时要对数以万计的图片搜索要求进行识别推断从而给出搜索结果;端侧推断更强调在高性能计算和低功耗中寻找一个平衡点,设计目标是低延时低功耗。

因此从目前市场需求来看,人工智能芯片可以分为三个类别:

用于训练(training)的芯片:主要面向各大AI企业及实验室的训练环节市场。目前被业内广泛接受的是“CPU+GPU”的异构模式,由于 AMD 在通用计算以及生态圈构建方面的长期缺位,导致了在深度学习 GPU 加速市场 NVIDIA 一家独大。面临这一局面,谷歌 2017年发布TPU 2.0能高效支持训练环节的深度网络加速。我们在此后进行具体分析;

用于云侧推断(inferenceoncloud)的芯片:在云端推断环节,GPU不再是最优的选择,取而代之的是,目前3A(阿里云、Amazon、微软 Azure)都纷纷探索“云服务器+FPGA”模式替代传统 CPU 以支撑推断环节在云端的技术密集型任务。但是以谷歌TPU为代表的ASIC也对云端推断的市场份额有所希冀;

参考观研天下发布《2018-2023年中国人工智能芯片市场发展现状与发展机遇分析报告》

用于端侧推断(inferenceondevice)的芯片:未来在相当一部分人工智能应用场景中,要求终端设备本身需要具备足够的推断计算能力,而显然当前 ARM 等架构芯片的计算能力,并不能满足这些终端设备的本地深度神经网络推断,业界需要全新的低功耗异构芯片,赋予设备足够的算力去应对未来越发增多的人工智能应用场景。我们预计在这个领域的深度学习的执行将更多的依赖于 ASIC。

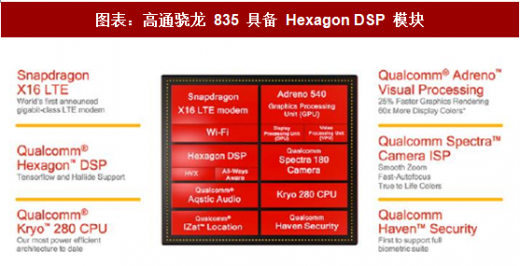

端侧 AI 芯片:SoC+IP 模式有望成为端侧主流。我们此前进行过介绍,未来在相当一部分人工智能应用场景中,要求终端设备本身需要具备足够的推断计算能力,而终端市场对芯片的功耗、面积、成本都有极为苛刻的要求。目前端侧人工智能芯片主要有独立ASIC和“SoC+IP”两种模式:

独立 ASIC:顾名思义,即研发设计、生产一款单独ASIC芯片用于深度神经网络加速,目前movidius的myriad系列芯片就是这种模式。其缺点在于开发周期长、投入成本大,一般公司难以承担;

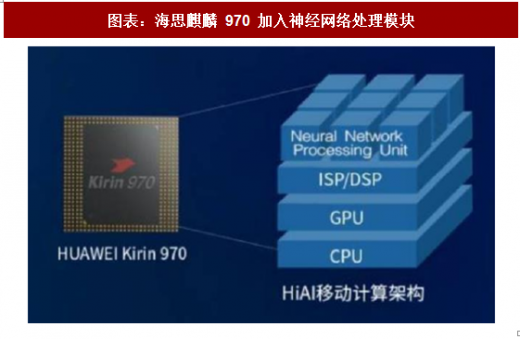

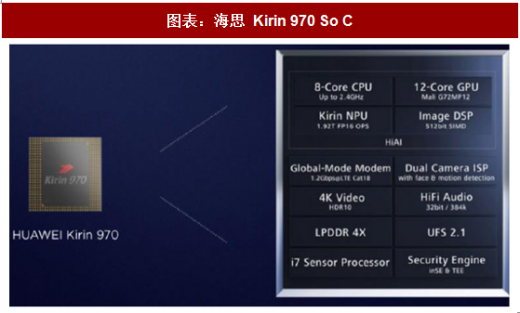

“SoC+IP”模式:这一模式将深度神经网络加速做成 IP,作为一个模块加入SoC。深度学习加速IP可以由专门公司开发、SoC厂购买,也可以由 SoC 厂自主开发。本质上与此前将 ISP、DSP、 GPU等模块加入SoC的历史类似,在成本、开发周期上具有极大优势,缺点则是功能拓展性有限;

我们认为“SoC+IP”模式有望成为主流。当深度神经网络加速功能做成 IP 时,它就成为 SoC 的一个模块,当 SoC 需要做深度学习相关运算时就交给该模块去做。因此对于深度学习加速领域的企业,能够更为灵活、更小投入地对深度学习加速产品进行开发和升级。近期发布的高通骁龙 835 与海思麒麟 970 均采用了这一模式。

目前,做深度学习加速IP的公司有Ceva、Cadence等等。这些公司的设计大多是基于已有的DSP架构,设计比较保守。也有如Kneron的初创公司试图用全新的加速器架构设计来满足应用的需求。

【版权提示】观研报告网倡导尊重与保护知识产权。未经许可,任何人不得复制、转载、或以其他方式使用本网站的内容。如发现本站文章存在版权问题,烦请提供版权疑问、身份证明、版权证明、联系方式等发邮件至kf@chinabaogao.com,我们将及时沟通与处理。